ELSEVIER

Contents lists available at ScienceDirect

# Microprocessors and Microsystems

journal homepage: www.elsevier.com/locate/micpro

# Anytime system level verification via parallel random exhaustive hardware in the loop simulation\*

Toni Mancini\*, Federico Mari, Annalisa Massini, Igor Melatti, Enrico Tronci

Computer Science Department, Sapienza University of Rome, Italy

#### ARTICLE INFO

#### Keywords:

Model Checking of Hybrid Systems Model checking driven simulation Hardware in the loop simulation

#### ABSTRACT

System level verification of cyber-physical systems has the goal of verifying that the *whole* (i.e., software + hardware) system meets the given specifications. Model checkers for hybrid systems cannot handle system level verification of actual systems. Thus, Hardware In the Loop Simulation (HILS) is currently the main workhorse for system level verification. By using model checking driven exhaustive HILS, System Level Formal Verification (SLFV) can be effectively carried out for actual systems.

We present a *parallel random exhaustive* HILS based model checker for hybrid systems that, by simulating *all* operational scenarios *exactly once* in a *uniform random* order, is able to provide, at *any time* during the verification process, an *upper bound* to the probability that the System Under Verification exhibits an error in a yet-to-be-simulated scenario (Omission Probability).

We show effectiveness of the proposed approach by presenting experimental results on SLFV of the Inverted Pendulum on a Cart and the Fuel Control System examples in the Simulink distribution. To the best of our knowledge, no previously published model checker can *exhaustively* verify hybrid systems of such a size and provide at *any time* an upper bound to the Omission Probability.

© 2015 Elsevier B.V. All rights reserved.

# 1. Introduction

The cost for fixing a design error in a system becomes larger and larger as the design proceeds from the requirement analysis to the implementation (see, e.g., [2, Chapter 1]) since the later in the design phase an error is detected the more reworking it may trigger. The above observation has motivated the development of methods and tools to verify correctness of a system already in the early phases of its design, namely during the requirement analysis or during the functional specification phases. The goal of all such approaches is to catch design errors well *before* the system implementation begins.

Of course, all such approaches are *model based*, that is they work on a model describing the system behaviour since no system implementation exists in the early design phases. Accordingly, *System Verification* is carried out by simulating a system model and analysing its behaviour under a *suitable set* of simulation scenarios.

For example, in a digital hardware setting, model based approaches have been used since a long time. In fact, even before

considering going to silicon, a heavy simulation activity is performed, aimed at verifying that the system model (defined, e.g., using Verilog, VHDL or SystemC<sup>1</sup>) meets the system requirements for most (possibly all) *uncontrollable inputs* (that is, *primary inputs* and *faults* the system is expected to withstand).

Along the same line of reasoning, in a purely software setting, before generating low level code, model based approaches are used to verify that the software model (defined, e.g., using AADL [3,4]) meets the given requirements.

If all possible simulation scenarios are considered, then we can prove *correctness* of the system (i.e., absence of simulation scenarios violating the system requirements), otherwise we can only show that the system design is faulty (by exhibiting a simulation scenario violating the system requirements). In other words, a *simulation campaign* that does not consider all possible simulation scenarios can only show that the system design has a bug. To show correctness of the system design we need an *exhaustive* simulation campaign, that is one considering all possible simulation scenarios. A verification approach able to show system correctness is usually referred to as *formal verification*. One of the most successful techniques to carry out formal verification is *Model Checking* (see, e.g., [5]).

$<sup>^{\</sup>scriptsize{\pm}}$  This paper is an extended and revised version of [1].

<sup>\*</sup> Corresponding author.

E-mail addresses: tmancini@di.uniroma1.it (T. Mancini), mari@di.uniroma1.it (F. Mari), massini@di.uniroma1.it (A. Massini), melatti@di.uniroma1.it (I. Melatti), tronci@di.uniroma1.it (E. Tronci).

http://www.mentor.com/products/fv/hdl\_designer/

The need for model checking stems from the high cost that a bug may have for certain systems. This is the case for *mission critical* systems, that is, systems for which a system malfunctioning may entail loss of money, as well as for *safety critical* systems, that is, systems for which a system malfunctioning may entail loss of human lives. Examples of mission critical systems are: decision support systems, satellites, processors (e.g., the infamous P5 FDIV bug costed about \$475 million to INTEL). Examples of safety critical systems are: railway interlocking, avionics control software.

Many Cyber-Physical Systems (CPSs) are indeed mission or safety critical systems. Accordingly, in this paper we focus on formal verification techniques for CPSs.

A CPS consists of hardware (e.g., motors, electrical circuits, etc.) and software components. Thus, in order to verify a CPS design, we need methods and tools that can model and effectively support simulation of hardware as well as software components.

From a formal point of view, CPSs can be modelled as hybrid systems (see, e.g., [6] and citations thereof). Many *Model Based Design* software tools offer support for modelling and simulation of CPSs. Well known examples are Simulink<sup>2</sup>, VisSim<sup>3</sup> and Modelica<sup>4</sup>. All such tools take as input a (mathematical) model of the behaviour of the CPS along with a simulation scenario and provide as output the time evolution (*trace* or *simulation run*) of the system at hand.

System Level Verification of CPSs aims at verifying that the whole (i.e., software + hardware) system meets the given specifications. System Level Formal Verification (SLFV) has the goal of exhaustively verifying that the above holds for all possible operational scenarios

For digital circuits, formal verification is usually carried out using model checking techniques (e.g., see [7]). Unfortunately, model checkers for hybrid systems cannot handle SLFV of real world CPSs. Thus, HILS is currently the main workhorse for system level verification of CPSs, and is supported by model based design tools (e.g., the previously mentioned Simulink, VisSim and Modelica).

In HILS, the *actual software* reads/sends values from/to mathematical models (*simulation*) of the physical systems (e.g., engines, analog circuits, etc.) it will be interacting with. Notwithstanding the word *hardware*, in HILS the only hardware present is the one devoted to support the system simulation, that is: computational and communication devices. This is because HILS is used in a model based design setting to validate the system design *before* any hardware is built (the whole goal of model based design). For example, Simulink, VisSim, Modelica, ESA Satellite Simulation Infrastructure SIMULUS<sup>5</sup> all provide simulation software supporting HILS, where the only hardware involved is just the computer on which the simulator is actually running.

Simulation can be very time consuming. Accordingly, in order to reduce system design time, Opal-RT<sup>6</sup> and dSpace<sup>7</sup> among others provide modelling and simulation software along with FPGA-based hardware to support real-time simulation. We note that in all cases the only hardware present in HILS is the one supporting the simulation itself.

#### 1.1. Motivations

SLFV is an exhaustive HILS where all relevant simulation scenarios are considered. Using a parallel model checking driven

approach, exhaustive HILS enables formal verification of actual systems. Examples of such systems are the Inverted Pendulum on a Cart (IPC) and the Fuel Control System (FCS) in the Simulink distribution (see Section 6.1.1).

Considering that parallel exhaustive HILS based SLFV may take days of computation (e.g., see [8]), from a practical point of view it would be very useful to have available at *any time* during the verification process, *quantitative* information about the degree of assurance attained. Such an information would enable us to evaluate if it is worth to continue the verification activity, or instead stop it since the degree of assurance attained can be considered adequate for the application at hand (*graceful degradation*).

The above considerations suggest looking for a HILS based model checking approach satisfying the following requirements: (i) it is *parallel*, in order to make exhaustive HILS computationally feasible; (ii) it is *exhaustive*, since our focus is SLFV; (iii) it is *any time*, to support *graceful degradation*.

The work in [9] presents a Propositional Satisfiability (SAT) based model checker for finite state systems which returns, at any time during the verification process, the coverage (i.e., the fraction of operational scenarios verified so far). Unfortunately, while coverage measures the amount of verification work done, it does not provide any information about the degree of assurance attained by the verification process. This is because formal verification aims at finding hard to find errors, i.e., errors that were not detected while verifying operational scenarios designed by experts. As a result, formal verification addresses the search of errors that we are unlikely to consider. For this reason, we can model the problem as an adversary system, that is a system where, knowing our verification strategy, the adversary places the error in operational scenarios we are less likely to visit. In such a framework, any deterministic ordering of the operational scenarios would not increase the degree of assurance until the end of the verification. In fact, the adversary would choose to place the single error in the last scenario picked by the verification procedure.

To provide a formally sound information about the degree of assurance attained by the verification process, approaches have been proposed which verify the operational scenarios in a *random* order. In particular, the work in [10] presents a Monte-Carlo based model checker for finite state systems that provides, at *any time* during the verification process, an upper bound to the probability that the System Under Verification (SUV) exhibits an error in a yet-to-be-simulated scenario (Omission Probability). The Omission Probability (OP) provides indeed the information we are looking for. Unfortunately, while Monte-Carlo based approaches guarantee randomness (thereby enabling OP computation) they are not exhaustive (within a finite time).

To the best of our knowledge, no model checker is available, neither for finite state systems nor for hybrid systems, which, at the same time, is both *random* and *exhaustive*, thereby enabling effective *anytime* SLFV. In this paper we advance the state of the art by presenting a *parallel random exhaustive* HILS based model checker along with experimental results showing its effectiveness.

#### 1.2. Main contribution

Our System Under Verification (SUV) is a *Hybrid System* (e.g., see [6] and citations thereof) whose inputs belong to a finite set of uncontrollable events (*disturbances*) modelling failures in sensors or actuators, variations in the system parameters, etc. We focus on *deterministic systems* (the typical case for control systems) and model nondeterministic behaviours (such as faults) with disturbances. Accordingly, in our framework, a *simulation scenario* is just a finite sequence of disturbances and a *simulation campaign* is a finite sequence of simulation instructions (namely: *save* a simulation state, *restore* a saved simulation state, *remove* a saved

<sup>&</sup>lt;sup>2</sup> http://www.mathworks.com.

<sup>&</sup>lt;sup>3</sup> http://www.vissim.com.

<sup>&</sup>lt;sup>4</sup> http://www.modelica.org.

$<sup>^{5}\</sup> http://www.esa.int/Our_Activities/Operations/gse/ESA_operations_software_licensable_products_-_overview .$

$<sup>^{\</sup>rm 6}$  http://www.opal-rt.com/about-hardware-loop-simulation .

<sup>&</sup>lt;sup>7</sup> https://www.dspace.com/en/inc/home.cfm .

simulation state, *inject* a disturbance, *advance* the simulation of a given time length).

A system is expected to *withstand* all disturbance sequences that may arise in its operational environment. Correctness of a system is thus defined with respect to such *admissible* disturbance sequences. In our setting, the set of admissible disturbance sequences (*disturbance model*) can be defined as the language accepted by a suitable Finite State Automaton, which in turn can be defined using the modelling language of any finite state model checker.

In such a framework we address *Bounded* SLFV of *safety* properties. That is, given a time step  $\tau$  (time quantum between disturbances) and a time horizon  $T=\tau h$  we return *PASS* if there is no *admissible* disturbance sequence of length h and time step  $\tau$  that violates the given safety property. We return *FAIL*, along with a counterexample, otherwise. Therefore, SLFV is an *exhaustive* (with respect to admissible disturbance sequences) HILS. In other words, we are aiming at (*black box*) bounded model checking where the SUV behaviour is defined by a simulator (Simulink in our examples).

In such a setting, our main contribution can be summarised as follows. We present an *anytime parallel random exhaustive* HILS based model checker that effectively conjugates exhaustiveness with randomness, thereby enabling the computation of the Omission Probability.

While a simulation run for digital hardware takes order of milliseconds on a normal desktop computer, in our setting a simulation run takes order of seconds since it entails heavy numerical computations aimed at solving a system of many *Ordinary Differential Equations* (modelling the hardware components of the CPS). Indeed (see Section 6) simulation of operational scenarios takes almost 100% of the overall verification time. Resting on such observation we build on the SLFV approach discussed in [8]. In particular:

- 1. From the disturbance model we generate all admissible simulation scenarios and evenly split them into disjoint sets (*slices*).

- 2. For each slice, we compute a highly optimised simulation campaign that exploits simulator save/restore/remove commands in order to save on the simulation time while scheduling execution of all simulation scenarios exactly once and in a uniform random order. This guarantees exhaustiveness and allows us to compute, at any time during the verification process, an upper bound to the OP.

- 3. We run simulation campaigns in parallel. This guarantees a very efficient parallelism, since no communication among processes is needed. This step is supported by simulation tools (Simulink in our case study).

We also show that, thanks to the fact that we have first generated all admissible simulation scenarios, attaining point 2 above (i.e., anytime OP computation) can be done in a *not-too-complicated* (from both technical and computational points of view) and *non-invasive way*, by simply introducing a new module into the workflow of [8] that seamlessly interoperates with the others.

## 1.3. Summary of experimental results

We implemented our approach and present (Section 6) experimental results on two case studies, namely the Inverted Pendulum on a Cart (IPC) and the Fuel Control System (FCS) examples in the Simulink distribution. Overall, we compute optimised simulation campaigns under four operational environments (disturbance models), which entail from 3 208 276 to 35 641 501 simulation scenarios.

Each processor (actually, a core of a 8-core machine) runs an instance of our (random) simulation campaign computation algorithm and takes as input a slice of our set of simulation scenarios. We present experimental results with 16, 32, 64 machines totalling 128, 256, 512 parallel processes. Our approach takes negligible time to generate an optimised simulation campaign for a given slice, with respect to the time needed to actually execute the simulation campaign (e.g., minutes vs. hours, see Section 6).

Our experimental results show that, by exploiting parallelism, our random exhaustive simulation campaigns effectively counteract the simulation time overhead due to randomisation. The above ensures feasibility of our parallel random exhaustive approach for actual systems, such as the Inverted Pendulum on a Cart (IPC) and Fuel Control System (FCS) examples in the Simulink distribution.

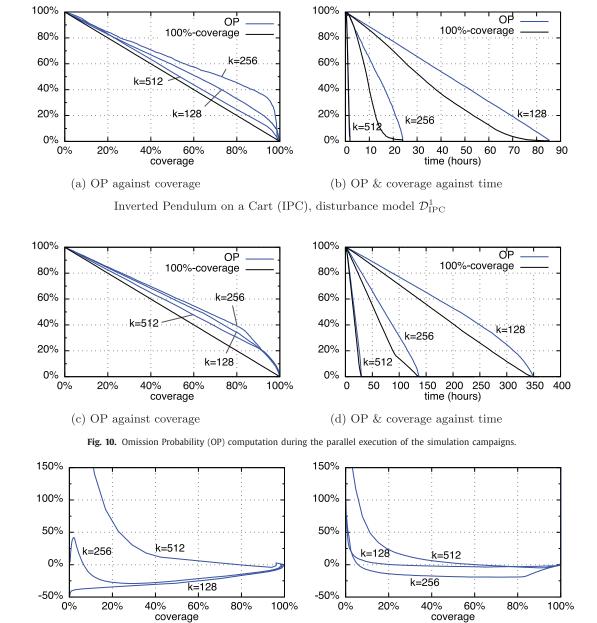

As for the Omission Probability (OP), the worst case scenario is when just one error trace is present. Our experimental results (Section 6.6) show that, even in such a case, our upper bound to the OP decreases about *linearly* with respect to the coverage, that is the fraction of scenarios simulated. This is the *best* one can hope to obtain in our setting.

Finally, simulation of scenarios in random order allows us to use the coverage as a reliable estimator for the *completion time* of the whole verification task. Our experimental results show that the error in the completion time estimation decreases quickly with respect to coverage.

### 1.4. Paper outline

Section 2 gives background notions to make our paper self-contained. Section 3 presents our formal framework, by formalising the notion of OP and by providing an upper bound for it, computable from the number of the yet-to-be-simulated traces in each slice. Section 4 outlines our algorithm which enables the computation, from a sequence (slice) of disturbance traces, a highly optimised simulation campaign which simulates the input traces in uniform random order and exploits the save/restore/remove capabilities of the simulator. Section 5 is devoted to the formal proofs of our results. Finally, Section 6 presents experimental results assessing effectiveness of our approach.

# 2. Background and preliminaries

In this section we give some background notions. Unless otherwise stated, all definitions are based on [8,11,12]. Throughout the paper, we use  $\mathbb{R}^{\geq 0}$  for the set of non-negative reals,  $\mathbb{R}^+$  for the set of strictly positive reals, and Bool =  $\{0,1\}$  for the set of Boolean values (0 for *false* and 1 for true).  $\mathbb{N}^+$  denotes the set of positive natural numbers.

# 2.1. Modelling the operational environment

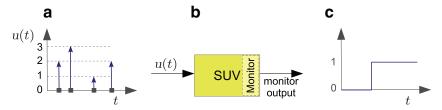

Our System Under Verification (SUV) is a Discrete Event System (DES), namely a continuous time Input-State-Output deterministic dynamical system [11] whose inputs are discrete event sequences. A discrete event sequence (Definition 1) is a function u(t) associating to each (continuous) time instant  $t \in \mathbb{R}^{\geq 0}$  a disturbance event (or, simply, disturbance). Disturbances, encoded by natural numbers in the interval [0, d] (for a given  $d \in \mathbb{N}^+$ ), represent uncontrollable events (e.g., faults). We use event 0 to represent the event carrying no disturbance. As no system can withstand an infinite number of disturbances within a finite time, we require that, in any time interval of finite length, a discrete event sequence u(t) differs from 0 only in a finite number of time points (Fig. 1a).

**Definition 1** (Discrete event sequence). Let  $d \in \mathbb{N}^+$ . A *discrete event sequence* over the natural interval [0, d] is a

Fig. 1. (a) A discrete event sequence (d=3); (b) Our SUV embedding a monitor; (c) The SUV monitor output.

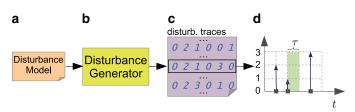

**Fig. 2.** (a) Disturbance model; (b) CMurphi-based disturbance generator; (c) Generated sequence of disturbance traces (d=3,h=6); (d) The discrete event sequence associated to the trace in the black rectangle in part (c), given time quantum  $\tau$ .

function  $u: \mathbb{R}^{\geq 0} \to [0,d]$  such that, for all  $t \in \mathbb{R}^{\geq 0}$ , the set  $\left\{ \tilde{t} \in \mathbb{R}^{\geq 0} \mid 0 \leq \tilde{t} \leq t \text{ and } u(\tilde{t}) \neq 0 \right\}$  has finite cardinality. We denote with  $\mathcal{U}_d$  the set of discrete event sequences over [0,d] (following control engineering notation for input functions to dynamical systems, see e.g. [11]).

In Definitions 2 and 3 we specify the concepts of *restriction* and *concatenation*, respectively, for functions belonging to  $\mathcal{U}_d$ .

**Definition 2.** Let  $\mathcal{U}_d$  be the set of discrete event sequences over the interval [0,d]. Given a function  $u\in\mathcal{U}_d$  and two real numbers  $0\leq t_1< t_2$ , we denote with  $u|_{[t_1,t_2)}$  the function  $u|_{[t_1,t_2)}:[t_1,t_2)\to [0,d]$ , such that  $u|_{[t_1,t_2)}(t)=u(t)$  for all  $t\in [t_1,t_2)$ . We denote  $\mathcal{U}_d^{[t_1,t_2)}$  the restriction of  $\mathcal{U}_d$  to the domain  $[t_1,t_2)$ .

**Definition 3.** Assume that  $t_1, t_2, t_3 \in \mathbb{R}^{\geq 0}$  such that  $t_1 < t_2 < t_3$ . If  $\omega \in \mathcal{U}_d^{[t_1,t_2)}$  and  $\omega' \in \mathcal{U}_d^{[t_2,t_3)}$ , their *concatenation*, denoted as  $\omega\omega'$ , is the function  $\tilde{\omega} \in \mathcal{U}_d^{[t_1,t_3)}$  defined as:

$$\tilde{\omega}(t) = \begin{cases} \omega(t) & \text{if } t \in [t_1, t_2) \\ \omega'(t) & \text{if } t \in [t_2, t_3) \end{cases}$$

System level verification follows an Assume-Guarantee approach aimed at showing that the SUV meets its specification (Guarantee) as long as the SUV operational environment behaves as expected (Assume). In this work we focus on bounded system level verification. As a consequence, we model (Definition 4) the SUV operations.

ational environment as the sequence of disturbances our SUV is expected to withstand within a *finite* time horizon, and we bound the *time quantum* between two consecutive disturbances.

**Definition 4** (Disturbance trace). Let  $h, d \in \mathbb{N}^+$ . An (h, d) disturbance trace  $\delta$  is a finite sequence  $\delta$ :  $[0, h-1] \to [0, d]$ . Given  $\tau \in \mathbb{R}^+$  (time quantum), an (h, d) disturbance trace  $\delta$  is univocally associated to a discrete event sequence  $u^\tau_\delta$ , defined as follows: for all  $t \in \mathbb{R}^{\geq 0}$ , if there exists  $j \in [0, h-1]$  such that  $t = \tau j$ , then  $u^\tau_\delta(t) = \delta(j)$ , else  $u^\tau_\delta(t) = 0$  (no disturbance).

Thus, a disturbance trace  $\delta$  defines an operational scenario (namely,  $u^{\tau}_{\delta}$ ) for our SUV. Fig. 2d shows the discrete event sequence associated to a disturbance trace. We represent our SUV operational environment as a finite set of (h,d) disturbance traces  $\Delta = \{\delta_0, \ldots, \delta_{n-1}\}$ , since  $U^{\tau}_{\Delta} = \{u^{\tau}_{\delta_0}, \ldots, u^{\tau}_{\delta_{n-1}}\}$  (for a given  $\tau \in \mathbb{R}^+$ ) defines the operational scenarios our SUV should withstand. Note that, by taking h large enough (as in Bounded Model Checking BMC) and  $\tau$  small enough (to faithfully model our SUV operational scenarios), we can achieve any desired precision. On such considerations rests the effectiveness of the approach.

As it is typically infeasible to define a SUV operational environment by explicitly listing all its disturbance traces, we define an operational environment with a *disturbance model* which is in turn defined as the language accepted by a suitable finite state automaton. The following example illustrates this point.

**Example 1.** Consider a disturbance model consisting of one disturbance (namely, a fault) which is always recovered within 4 s (i.e., 4 seconds). Let us assume that between two consecutive disturbances (faults) there must be at least 5 s and that disturbances can arise only at time steps multiple of  $\tau = 1$  s (*time quantum*). We also assume that the verification time horizon is set to 6 s.

In Fig. 3a we show disturbance traces represented as strings of zeros (no disturbance) and ones (disturbance), with time flowing from left to right. The 8 strings terminated by  $\sqrt{}$  denote all the disturbance traces accepted by the disturbance model (admissible

```

\begin{array}{ccc} 000000\sqrt{} & 010000\sqrt{} \\ 000001\sqrt{} & 010001\otimes \\ 000010\sqrt{} & 01001\otimes \\ 0000100\sqrt{} & 011\otimes \\ 000100\sqrt{} & 011\otimes \\ 000101\otimes & 100000\sqrt{} \\ 00011\otimes & 100001\sqrt{} \\ 001000\sqrt{} & 10001\otimes \\ 001001\otimes & 1001\otimes \\ 00101\otimes & 101\otimes \\ 00110\otimes & 11\otimes \\ \end{array}

```

(a) Admissible disturbance traces ( $\sqrt{}$ ) and shortest disturbance sequences that cannot be extended to an admissible disturbance trace ( $\otimes$ )

```

function disturbanceModel(h)

cnt \leftarrow 0; /* counter */

t \leftarrow 0; /* time */

while t \le h do

d \leftarrow read(); t \leftarrow t+1;

if cnt > 0 then cnt \leftarrow cnt-1;

if d=1 then

if cnt > 0 then return \otimes;

else cnt \leftarrow 4;

return \sqrt{};

end

(b) Finite state automaton recognising t

```

(b) Finite state automaton recognising the language of admissible disturbance traces (disturbance model)

Fig. 3. Example 1.

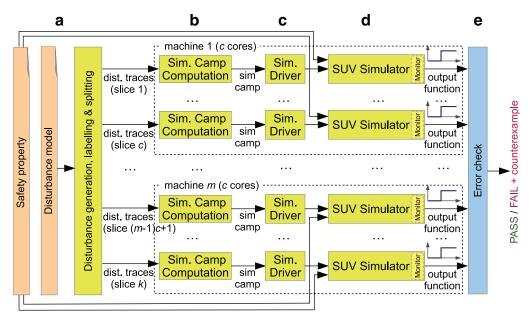

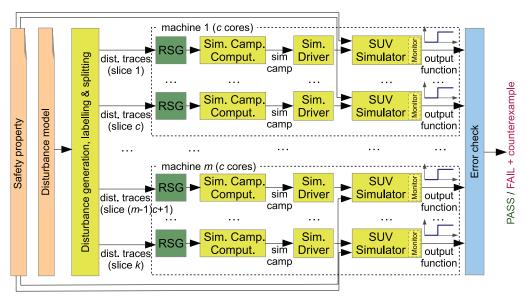

**Fig. 4.** Parallel HILS based dSLFV [8]: k parallel processes are run on m multi-core machines (we show a possible deployment with machines having c cores each, i.e., k = mc).

disturbance traces). The 14 strings terminated by  $\otimes$  are the shortest non-admissible sequences of disturbances, that is disturbance sequences that *cannot* be extended to admissible disturbance traces.

Fig. 3b shows the pseudo-code for a finite state automaton recognising such a language.

We define a finite state automaton for a disturbance model using the modelling language of a finite state model checker (namely, CMurphi [13]), along the lines of [8].

# 2.2. Modelling the property to be verified

Along the lines of [14], we model the property to be verified with a continuous-time *monitor* which observes the state of the system to be verified and checks whether the property under verification is satisfied (Fig. 1b). The output of the monitor is 0 as long as the property under verification is satisfied and becomes and stays 1 (*sustain*) as soon as the property fails, thus ensuring that we never miss a property failure report, even when sampling the monitor output only at discrete time points (Fig. 1c). The use of monitors gives us a flexible approach to model the property to be verified. In particular, it is easy to model bounded safety and bounded liveness properties as monitors. Figs. 8 and 9 show the Simulink/Stateflow representations of our two case studies (Inverted Pendulum on a Cart and Fuel Control System, respectively), along with their property monitors (see Section 6).

# 2.3. Modelling the SUV

Since the monitor output is all we need to carry out our verification task, we can model our SUV *along with* the property to be verified as a DES with an *embedded* monitor (Fig. 1b). We call *Monitored Discrete Event System (MDES)* such a DES.

According to our *black-box* approach to SUV modelling, given a time quantum  $\tau \in \mathbb{R}^+$ , Definition 5 formalises an (h, d) MDES as a function  $\mathcal{H}$  associating, to each (h, d) disturbance trace  $\delta$ , a Boolean value  $\mathcal{H}(\delta)$  representing the output of the SUV monitor at time  $T = \tau h$  (the time horizon), when the system (starting from its initial state) is given as input the discrete event sequence  $u_{\delta}^{\tau}(t)$  associated to  $\delta$ . For any disturbance trace  $\delta$ ,  $\mathcal{H}(\delta)$  is 1 (*error*) if and

only if  $u_{\delta}^{\tau}(t)$  *violates* the property under verification within time horizon  $T = \tau h$  (with the SUV starting from its initial state).

**Definition 5.** ((h, d) **Monitored DES)** Let  $h, d \in \mathbb{N}^+$ . A (h, d) *Monitored Discrete Event System (MDES)* is a function  $\mathcal{H}$ : ([0, h-1]  $\rightarrow$  [0, d])  $\rightarrow$  Bool mapping all (h, d) disturbance traces to Boolean values.

#### 2.4. System Level Formal Verification (SLFV)

Definition 6 formalises our bounded System Level Formal Verification problem.

**Definition 6.** A System Level Formal Verification (SLFV) problem is a tuple  $P = (h, d, \Delta, \mathcal{H})$  where:  $h, d \in \mathbb{N}^+, \Delta = \{\delta_0, \ldots, \delta_{n-1}\}$  is an (h, d) set of disturbance traces, and  $\mathcal{H}$  is a (h, d) MDES.

The *answer* to SLFV problem *P* is *FAIL* if there exists a disturbance trace  $\delta$  in  $\Delta$  such that  $\mathcal{H}(\delta) = 1$  (in such a case also the *counterexample*  $\delta$  is returned), *PASS* otherwise.

Note that, notwithstanding the fact that the number of states of our SUV is infinite and we are in a continuous time setting, to answer a SLFV problem we only need to check a *finite* number of disturbance traces. This is because we are bounding: (a) our time horizon to  $T=\tau h$ , and (b) the set of time points at which disturbances can take place, by taking  $\tau$  as the time quantum among disturbance events.

# 2.5. Parallel HILS based deterministic SLFV

In the black-box parallel approach shown in [8], the MDES  $\mathcal H$  defining our SUV (plus the property to be verified) is defined using the modelling language of a suitable simulator (e.g., MatLab and Stateflow for Simulink). The answer to a SLFV problem  $(h, d, \Delta, \mathcal H)$  is computed by simulating each operational scenario  $\delta$  in the operational environment  $\Delta$ , thus by performing an exhaustive (with respect to  $\Delta$ ) Hardware In the Loop Simulation (HILS). The overall workflow is shown in Fig. 4 and described in the remainder of this section. We will refer to this approach as Deterministic SLFV (dSLFV), where the word "deterministic" stems from the fact that the disturbance traces are verified in a deterministic order.

```

a0b2c1d0e0f1g

store(a)

a0b2c2h0i0j0k

load(\mathbf{a}) run(0,1) store(\mathbf{b}) run(2,1) store(\mathbf{c}) run(1,3) run(1,1)

load(\mathbf{c}) run(2,2) store(\mathbf{i}) run(0,2)

a0b2c2h0i3m0n

load(i) free(i) run(3,2)

a0b2c3p1q1r0s

load(\mathbf{c}) run(3,1) store(\mathbf{p}) run(1,1) run(1,2)

a0b2c3p2v2w0x

load(\mathbf{p}) free(\mathbf{p}) free(\mathbf{c}) run(2,1) run(2,2)

a0b3y0z0\alpha1\beta0\lambda

load(b) free(b) free(a) run(3,3) run(1,2)

(a) A sequence of labelled disturbance

(b) Optimised simulation campaign which simulates

traces (labels in red, disturbances in

the sequence of disturbance traces in (a) in their nat-

```

Fig. 5. Labelled disturbance traces and optimised simulation campaign.

## 2.5.1. Disturbance trace generation and splitting

Our CMurphi-based trace generator (see Section 2.1 and Fig. 4a) works in Depth-First Search (DFS) mode, and, given the set of disturbances, produces a sequence  $\Delta$  of n disturbance traces. Each generated trace  $\delta$  in  $\Delta$  is annotated with *labels* and is of the form  $\delta = (l_0, \ d_0, \ l_1, \ d_1, \dots, \ l_{h-1}, \ d_{h-1}, \ l_h)$ , where  $\delta = (d_0, \dots, d_{h-1})$  is a sequence of disturbances satisfying the disturbance model and  $l_0, \dots, l_h$  belong to a countable set of *labels* L.

Labels are defined by an *injective map*  $\lambda$  from finite sequences of disturbances (including the empty sequence) to L. Label  $l_0$  is common to all traces and it is associated to the simulator initial state. Prefixes of disturbance sequences  $(\hat{d_0},\ldots,\hat{d_{p-1}})$  common to multiple disturbance traces in  $\Delta$  are followed by the *same* label  $\hat{l}_p = \lambda(\hat{d_0},\ldots,\hat{d_{p-1}})$ . Fig. 5a shows a short sequence of labelled disturbance traces.

Labels identifying common disturbance prefixes are essential in the efficient computation of optimised simulation campaigns. Note that, given that our CMurphi-based generator runs in DFS mode, disturbance traces can be labelled at *no additional computational cost* during generation. Trace labelling during generation greatly increases the efficiency of the simulation campaign optimiser, as shown in [8].

In the following, we will use  $\delta^{\lambda}$  instead of  $\delta$  (respectively,  $\Delta^{\lambda}$  instead of  $\Delta$ ) when we want to emphasise that a trace  $\delta$  is annotated (respectively, all traces in set  $\Delta$  are annotated) with labels, or when we need such labels. In order to enable parallel verification via  $k \in \mathbb{N}^+$  processes, we evenly partition the sequence of labelled disturbance traces  $\Delta^{\lambda}$  into  $k \in \mathbb{N}^+$  sequences of disturbance traces  $\Delta^{\lambda}$ , . . . ,  $\Delta^{\lambda}_{k-1}$  (called *slices*).

$\Delta_0^\lambda,\ldots,\Delta_{k-1}^\lambda$  (called *slices*). The splitting process produces slices containing  $\lceil n/k \rceil$  traces each, except the last slice, which may contain fewer traces if n is not a multiple of k.

# 2.5.2. Computation of optimised simulation campaigns

In the next phase of the workflow in Fig. 4, we use the k slices  $\Delta_0^\lambda,\ldots,\Delta_{k-1}^\lambda$  generated so far to compute, independently and in parallel, k highly optimised simulation campaigns (Fig. 4b). Such simulation campaigns can be simulated, again independently and in parallel, using k simulators, each one running (e.g., on a different core of a bunch of multi-core machines) a model for  $\mathcal{H}$  (Fig. 4c-d).

The *answer* to the SLFV problem is *FAIL* if one of the simulation campaigns raises the simulator output function to 1 (in this case the disturbance trace  $\delta$  which raised the error is returned as a *counterexample*, see Fig. 4e). The answer is *PASS* otherwise.

Each simulator accepts four basic commands: store, load, free, run. Command store(l) stores in memory the current state of the simulator and labels with l such a state. Command load(l) loads into the simulator the stored state labelled with l. Command free(l) removes from the memory the state labelled with l. Command run(e, t) (with  $e \in [0, d]$  and  $t \in \mathbb{R}^+$ ) injects disturbance e and then advances the simulation of time e. A e simulation e campaign is thus a sequence of simulator commands.

The simulation campaign  $\chi_i$   $(0 \le i < k)$  computed from input slice  $\Delta_i^{\lambda}$  steers the simulator as to execute all disturbance traces in  $\Delta_i^{\lambda}$  according to their order in the slice (this is the reason why we refer to this approach as Deterministic SLFV).

Each disturbance trace is executed as if starting from the simulator initial state. However, by using commands *store* and *load*, the optimiser avoids revisiting simulation states as much as possible (as in explicit model checking). Using command *free* the optimiser removes from the simulator memory states that will never be needed in the remaining part of the simulation campaign. This is needed since each state may require many KB of memory (150–300 KB in the case studies presented in this paper).

Fig. 5b shows the optimised simulation campaign computed from the sequence of labelled disturbance traces in Fig. 5a, in the simple case where we ignore any limit on number of states that can be kept simultaneously stored in the simulator memory.

## 3. Omission Probability

This section formally defines the notion of Omission Probability (OP) (Definitions 7 and 8) and provides an upper bound for it, which can be computed anytime *during* the parallel verification process from the number of the yet-to-be-simulated traces in each slice (Theorem 1).

**Notation 1** (Set of permutations of a set). Let  $\Delta = \{\delta_0, \dots, \delta_{n-1}\}$  be a finite non-empty set. We denote with  $Perm(\Delta)$  the set of permutations of elements of  $\Delta$ :

$$\operatorname{Perm}(\Delta) = \left\{ (\theta_0, \dots, \theta_{n-1}) \mid (\forall i \in [0, n-1] \ \theta_i \in \Delta) \right.$$

$$\land (\forall i, j \in [0, n-1] \ i \neq j \rightarrow \theta_i \neq \theta_j) \right\}$$

If

$$\hat{\Delta} = (\delta_0, \dots, \delta_{n-1}) \in \text{Perm}(\Delta)$$

we write also  $\hat{\Delta}(i)$  for  $\delta_i$ .

A Random Sequence Generator (RSG) models the *extraction* of a random permutation from a given finite non-empty set (which, in our case, will be the set of admissible disturbance traces  $\Delta$ ). This is formalised in Definition 7.

**Definition 7** (Random Sequence Generator). Let  $\Delta$  be a finite nonempty set. A Random Sequence Generator (RSG) for  $\Delta$  is a probability space  $(\Omega, \mathcal{F}, Pr)$ , where:

- $\Omega$  (the space of *outcomes*) is the set of permutations of  $\Delta$ , that is  $\Omega = \text{Perm}(\Delta)$ .

- $\mathcal{F}$  (the space of *events*) is the set of subsets of  $\Omega$ , that is:  $\mathcal{F} = 2^{\Omega} = \{E \mid E \subseteq \Omega\}$ .

- $\Pr: \mathcal{F} \to [0,1]$  is a probability measure such that, for all  $\omega \in \Omega$ ,  $\Pr(\omega) = \frac{1}{|\Delta|!}$ . That is, permutations of  $\Delta$  are extracted with uniform probability. Since  $\Omega$  is countable (actually finite), the probability of any event  $E \in \mathcal{F}$  is defined as  $\Pr(E) = \sum_{\omega \in E} \Pr(\omega)$ .

Let  $(\Delta_0,\ldots,\Delta_{k-1})$  be a partition of  $\Delta$  into  $k\in\mathbb{N}^+$  disjoint non-empty sets. For any  $0\leq i< k$ , let  $(\Omega_i,\mathcal{F}_i,\Pr_i)$  be a RSG for  $\Delta_i$ . A Random Sequence Generator for  $(\Delta_0,\ldots,\Delta_{k-1})$  is a

probability space  $(\Omega, \mathcal{F}, \Pr)$ , where:  $\Omega = \times_{i=0}^{k-1} \Omega_i$ ,  $\mathcal{F} = \times_{i=0}^{k-1} \mathcal{F}_i$  and, for each event  $E_0 \times \dots \times E_{k-1} \in \mathcal{F}$   $(E_i \in \mathcal{F}_i$  for each  $0 \le i < k)$ ,  $P(E_0 \times \dots \times E_{k-1}) = \prod_{i=0}^{k-1} \Pr_i(E_i)$ .

Note that, by Definition 7, a RSG for a partition  $(\Delta_0,\ldots,\Delta_{k-1})$  of  $\Delta$  models the extraction of k permutations of, respectively,  $\Delta_0,\ldots,\Delta_{k-1}$ . For all  $0\leq i< k$ , the extracted permutation of  $\Delta_i$  is chosen *uniformly* among all possible permutations of  $\Delta_i$ . Also, the k permutations are extracted *independently* from each other.

Definition 8 defines the probability of omitting the simulation of a trace  $\bar{\delta} \in \Delta$  containing an error (i.e.,  $\mathcal{H}(\bar{\delta}) = 1$ ) when the verification process has *already* examined  $q_i$  disturbance traces, where  $q_i \in \{0, \dots, |\Delta_i|\}$ , from a random permutation of slice  $\Delta_i$ , for all  $0 \le i < k$ . Thus  $q_i$  represents the state of advancement of the computation on the ith slice  $\Delta_i$ . Hence  $(q_0, \dots, q_{k-1})$  defines the state of advancement (stage) of the computation on all slices. We denote this probability as Omission Probability (OP).

**Definition 8** (Omission Probability). Let  $(h, d, \Delta, \mathcal{H})$  be a System Level Formal Verification (SLFV) problem and  $(\Delta_0, \ldots, \Delta_{k-1})$  be a partition of  $\Delta$  into  $k \in \mathbb{N}^+$  disjoint non-empty sets. Let  $(\Omega, \mathcal{F}, \Pr)$  be a RSG for  $(\Delta_0, \ldots, \Delta_{k-1})$ , and  $(q_0, \ldots, q_{k-1})$  a tuple such that  $q_i \in \{0, \ldots, |\Delta_i|\}$  for each  $0 \le i < k$ .

The *Omission Probability (OP)* for  $(\Delta_0, \ldots, \Delta_{k-1})$  at stage  $(q_0, \ldots, q_{k-1})$ , is defined as:

$$\begin{aligned} & OP_{\mathcal{H}}(|\Delta_0|,\ldots,|\Delta_{k-1}|,q_0,\ldots,q_{k-1}) \\ & = \Pr\left( \left\{ (\omega_0,\ldots,\omega_{k-1}) \middle| & \begin{array}{l} \forall i \in [0,k-1] \ \omega_i \in \Omega_i \land \\ & AB((\omega_0,\ldots,\omega_{k-1}),(q_0,\ldots,q_{k-1})) \end{array} \right\} \right) \end{aligned}$$

where:

- AB is defined as  $A((\omega_0,\ldots,\omega_{k-1}),(q_0,\ldots,q_{k-1})) \land B((\omega_0,\ldots,\omega_{k-1}),(q_0,\ldots,q_{k-1}))$

- A (After) is:  $A((\omega_0, ..., \omega_{k-1}), (q_0, ..., q_{k-1})) = \exists i \in [0, k-1] \exists j \in [q_i, |\Delta_i|] \ \mathcal{H}(\omega_i(j)) = 1;$

- B (Before) is:  $B((\omega_0, ..., \omega_{k-1}), (q_0, ..., q_{k-1})) = \forall i \in [0, k-1] \ \forall j \in [0, q_i-1] \ \mathcal{H}(\omega_i(j)) = 0.$

In Definition 8, formula A (After) states that there exists a yet-to-be-simulated trace  $\bar{\delta}$  (some trace  $j \geq q_i$  of some slice i) containing an error, i.e., such that  $\mathcal{H}(\bar{\delta})$  evaluates to 1. Formula B (Before) states that none of the already simulated traces contains an error, i.e., function  $\mathcal{H}$  evaluates to 0 for all of them.

The following Theorem 1 gives an upper bound to the OP, after having simulated  $q_i$  randomly extracted traces from slice  $\Delta_i$  (for each  $0 \leq i < k$ ). In particular, Theorem 1 provides a bound to the probability of omitting the simulation of a trace  $\bar{\delta} \in \Delta$  containing an error when the verification process has already examined  $q_i$  disturbance traces from the (the permutation of) slice  $\Delta_i$  (for all  $0 \leq i < k$ ). Importantly, the bound provided does *not* depend on  $\mathcal{H}$ , i.e., it is *independent* of the system model. The proof of the theorem is in Section 5.

**Theorem 1.** Let  $(h, d, \Delta, \mathcal{H})$  be a SLFV problem and  $(\Delta_0, \ldots, \Delta_{k-1})$  be a partition of  $\Delta$  into  $k \in \mathbb{N}^+$  disjoint non-empty sets. Let  $(\Omega, \mathcal{F}, \Pr)$  be a Random Sequence Generator for  $(\Delta_0, \ldots, \Delta_{k-1})$  and  $(q_0, \ldots, q_{k-1})$  a tuple such that  $q_i \in \{0, \ldots, |\Delta_i|\}$  for each  $0 \le i < k$ . We have:

$$OP_{\mathcal{H}}(|\Delta_0|, \dots, |\Delta_{k-1}|, q_0, \dots, q_{k-1}) \le 1 - \min\left\{\frac{q_i}{|\Delta_i|} | 0 \le i < k\right\}$$

(1)

Note that the construction of the slices  $\Delta_0,\ldots,\Delta_{k-1}$  from  $\Delta$  is non-deterministic (i.e., any partitioning of  $\Delta$  would work), whereas, for each slice, the selection of a permutation is a probabilistic process, modelled as a RSG. Accordingly, Theorem 1 bounds the OP using the worst case distribution, i.e., the distribution yielding the

greatest OP. From this stems the min function in the right member of the inequality in Theorem 1.

Finally, we observe that, from Theorem 1, it follows that  $OP_{\mathcal{H}}(|\Delta_0|,\ldots,|\Delta_{k-1}|,|\Delta_0|,\ldots,|\Delta_{k-1}|)=0$ , that is, our verification task terminates after  $\max\{|\Delta_i|\mid 0\leq i< k\}$  parallel steps, having simulated all traces in  $\Delta$ .

# 4. Enabling Omission Probability computation: random exhaustive SLFV

Our disturbance trace generator (see Section 2.1) produces a sequence of disturbance traces  $\Delta^{\lambda}$ , whose order is deterministically chosen by the employed algorithm (in our case, Depth-First Search (DFS)). As a consequence, no information about the Omission Probability (OP) can be inferred *during* the verification process if the simulation campaign computed from each slice verifies the sequence of disturbance traces therein according to their order (as done by the Deterministic SLFV (dSLFV) approach of Section 2.5), or according to *any deterministic* order, as argued in Section 1.1.

From Section 3 it follows that it is possible to enable OP computation (and hence, *graceful degradation* during the computationally very expensive simulation phase) by simulating the disturbance traces within each slice in an order uniformly chosen at random.

Here we show how we can add support to OP computation in the workflow of Fig. 4 in a *not-too-complicated* and *non-invasive* way, by introducing an additional step, in the parallel portion of the workflow, which implements a Random Sequence Generator (RSG).

The new workflow, which we refer to as random exhaustive SLFV (rSLFV), is shown in Fig. 6. All slices are given as input, in parallel, to instances the new Random Sequence Generator module, shown as Algorithm 1. The Random Sequence Generator module reads a sequence of disturbance traces and computes a random permutation of it, uniformly chosen among all possible permutations, thus implementing a RSG (Definition 7). We argue that the introduction of the new Random Sequence Generator module is non-too-complicated for what concerns both its implementation (Algorithm 1) and its computational viability (see Section 6.3). It is also non-invasive, as it seamlessly interoperates with the dSLFV workflow of Section 2.5.

As the input sequence can be too large to be kept in main memory, the Random Sequence Generator module implements a disk-based multi-round algorithm (shown as Algorithm 1) which takes efficiency into account by using, in each round, as much main memory as possible and by reading/writing the input/output trace files sequentially.

Let  $n=|\Delta^{\lambda}|$  be the number of disturbance traces in the input sequence. Given parameter  $z\in\mathbb{N}^+$  for the maximum number of disturbance traces which can be simultaneously stored in main memory, the algorithm, at each round  $r\geq 1$ , selects the z traces which will have output positions in the interval  $[(r-1)z, \min(n, rz-1)]$ .

The above selection is performed by computing the first z elements of a random permutation of the traces not yet in the output file  $\Delta_{\rm rnd}^{\lambda}$ , chosen uniformly among all possible permutations. Such a permutation prefix is computed by function rndPermPrefix() (Algorithm 1, from line 20). Function rndPermPrefix() performs a swap-based computation of a permutation of integers  $[0, |\Delta_{\rm in}^{\lambda}| - 1]$  (uniformly chosen at random) and interrupts the computation as soon as the first z elements (see variable result) have been determined. During its operation, function rndPermPrefix() represents the partially computed permutation as an associative array perm, which, at any step of the function execution, represents

Fig. 6. Parallel HILS based rSLFV.

permutation  $\pi$  of [0, n-1] such that, for each  $j \in [0, n-1]$ :

$$\pi\left(j\right) = \begin{cases} v & \text{if} \quad (j,v) \in \textit{perm} \\ j & \text{otherwise, i.e., } \not\exists v \; (j,v) \in \textit{perm} \end{cases}$$

The main algorithm then appends the z randomly selected traces (as chosen by function rndPermPrefix()) to  $\Delta^{\lambda}_{rnd}$  (according to their output positions), and dumps all the others to a temporary file, which becomes the input of the next round. Algorithm 1 terminates in  $\lceil n/z \rceil$  rounds.

The following theorem asserts that Algorithm 1, when applied to a sequence of disturbance traces  $\Delta^{\lambda}$ , produces a uniformly chosen permutation over the set of all permutations. The proof of the theorem is in Section 5.

**Theorem 2.** Let  $\Delta^{\lambda}$  be a file containing n disturbance traces. For any  $z \geq 1$ , Algorithm 1 stores in file  $\Delta^{\lambda}_{rnd}$  a permutation of the traces in  $\Delta^{\lambda}$  extracted with uniform probability among all possible permutations.

The k output randomised slices (computed in parallel by k instances of the Random Sequence Generator algorithm from k input slices) are then given as input to k parallel instances of the simulation campaign computation module described in Section 2.5.2 which compute k highly optimised simulation campaigns (Fig. 6). As each simulation campaign verifies the traces in its input slice according to the their order, the introduction of the Random Sequence Generator module effectively enforces a random order in the disturbance trace verification within each slice, satisfying the requirements stated in Theorem 1 in order to compute, during simulation, an upper bound to the OP.

# 5. Proof of results

**Theorem 1.** Let  $(h, d, \Delta, \mathcal{H})$  be a System Level Formal Verification (SLFV) problem and  $(\Delta_0, \ldots, \Delta_{k-1})$  be a partition of  $\Delta$  into  $k \in \mathbb{N}^+$  disjoint non-empty sets. Let  $(\Omega, \mathcal{F}, \operatorname{Pr})$  be a Random Sequence Generator for  $(\Delta_0, \ldots, \Delta_{k-1})$  and  $(q_0, \ldots, q_{k-1})$  a tuple such that  $q_i \in \{0, \ldots, |\Delta_i|\}$  for each  $0 \le i < k$ . We have:

$$OP_{\mathcal{H}}(|\Delta_0|, \dots, |\Delta_{k-1}|, q_0, \dots, q_{k-1}) \le 1 - \min\left\{\frac{q_i}{|\Delta_i|} | 0 \le i < k\right\}$$

(1)

**Proof.** If, for all  $\delta \in \Delta$ ,  $\mathcal{H}(\delta) = 0$ , then the left member of (1) is  $\Pr(\emptyset) = 0$  and the thesis follows.

Otherwise, let E be a nonempty set containing *error traces*, that is  $E = \{\delta \mid \delta \in \Delta \land \mathcal{H}(\delta) = 1\} \neq \emptyset$ .  $OP_{\mathcal{H}}(|\Delta_0|, \ldots, |\Delta_{k-1}|, q_0, \ldots, q_{k-1})$  can be rewritten as (see Definition 8):

$$\Pr(\{(\omega_0, \dots, \omega_{k-1}) \mid \forall i \in [0, k-1] \ \omega_i \in \Omega_i$$

$$\land \forall i \in [0, k-1] \ \forall j \in [0, q_i-1] \ \omega_i(j) \notin E\})$$

(2)

because  $(\Delta_0, \ldots, \Delta_{k-1})$  is a partition of  $\Delta$ .

Consider any  $\bar{\delta} \in E$ . Probability (2) is less than or equal to

$$\Pr(\{(\omega_0, \dots, \omega_{k-1}) \mid \forall i \in [0, k-1] \ \omega_i \in \Omega_i$$

$$\land \forall i \in [0, k-1] \ \forall j \in [0, q_i-1] \ \omega_i(j) \neq \bar{\delta}\})$$

(3)

Given that  $\bar{\delta}$  belongs to exactly one of  $\Delta_0,\ldots,\Delta_{k-1}$ , say  $\Delta_{\bar{i}}$ , and given the definition of  $\Pr(\omega_0,\ldots,\omega_{k-1})$  in Definition 7, expression (3) is equal to:

$$\left(\prod_{\substack{i=0\\i\neq i}}^{k-1} \Pr\left(\{\omega_i \in \Omega_i\}\right)\right) \times \Pr\left(\{\omega_{\bar{i}} \in \Omega_{\bar{i}} \mid \forall j \in [0, q_{\bar{i}}-1] \ \omega_{\bar{i}}(j) \neq \bar{\delta}\}\right)$$

which is equal to

$$\Pr(\left\{\omega_{\bar{i}} \in \Omega_{\bar{i}} \mid \forall j \in [0, q_{\bar{i}} - 1] \ \omega_{\bar{i}}(j) \neq \bar{\delta}\right\}) \tag{4}$$

as, for each  $i \neq \overline{i}$   $(0 \leq i < k)$ ,  $Pr(\{\omega_i \in \Omega_i\}) = 1$ .

Probability (4) is the probability of picking a permutation  $\omega_{\tilde{i}}$  of  $\Delta_{\tilde{i}}$  which does not have  $\tilde{\delta}$  in the first  $q_{\tilde{i}}$  positions, and evaluates to  $1-\frac{q_{\tilde{i}}(|\Delta_{\tilde{i}}|-1)!}{|\Delta_{\tilde{i}}|!}=1-\frac{q_{\tilde{i}}}{|\Delta_{\tilde{i}}|}$  which is less than or equal to  $1-\min\{\frac{q_{i}}{|\Delta_{\tilde{i}}|}|0\leq i< k\}$ . The thesis follows.  $\square$

**Theorem 2.** Let  $\Delta^{\lambda}$  be a file containing n disturbance traces. For any  $z \geq 1$ , Algorithm 1 stores in file  $\Delta^{\lambda}_{rnd}$  a permutation of the traces in  $\Delta^{\lambda}$  extracted with uniform probability among all possible permutations.

**Proof.** We prove the following: (i) all traces in the input sequence (file  $\Delta^{\lambda}$ ) will occur in the output sequence (file  $\Delta^{\lambda}_{rnd}$ ) exactly once (i.e., the algorithm computes a permutation); (ii) for each  $\delta$  occurring in  $\Delta^{\lambda}$ , the probability that  $\delta$  occurs in  $\Delta^{\lambda}_{rnd}$  at any position is  $\frac{1}{n}$  (i.e., the computed permutation is uniformly extracted among all possible permutations).

# Algorithm 1 Random Sequence Generator.

```

Input: \Delta^{\lambda}, a file holding a labelled sequence of disturbance traces

Output: \Delta_{\text{rnd}}^{\lambda}, a file holding a random permutation of disturbance traces,

uniformly chosen among all possible permutations

1 param z, max # of traces that can be kept in RAM

2 \Delta_{rnd}^{\lambda} \leftarrow a new empty file;

3 \Delta^{\lambda}_{tmp} \leftarrow \Delta^{\lambda}; /* input of 1st round */

4 r \leftarrow 1; /* round counter */

5 while \Delta^{\lambda}_{tmp} is not empty do

\Delta^{\lambda}_{in} \leftarrow \hat{\Delta^{\lambda}_{tmp}}; /* tmp file of prev. round */

\Delta^{\lambda}_{tmp} \leftarrow \text{a new temp file; } /* \text{ next round input *} /

if z > |\Delta^{\lambda}_{in}| then z \leftarrow |\Delta^{\lambda}_{in}|;

selected\_pos \leftarrow rndPermPrefix(|\Delta^{\lambda}_{in}|, z); /* selected\_pos is a mapping from

[0, z-1] to [0, |\Delta^{\lambda}_{in}|-1] */

selected\_traces \leftarrow empty array of z elements;

10

11

p \leftarrow 0;

foreach \delta \in \Delta^{\lambda}_{in} do

12

if \exists i \text{ selected\_pos}[i] = p \text{ then } \text{ selected\_traces}[i] \leftarrow \delta;

13

else append trace \delta to \Delta^{\lambda}_{tmp};

14

p \leftarrow p + 1;

15

for i \leftarrow 0 \dots z - 1 do

16

append trace selected_traces[i] to \Delta_{rnd}^{\lambda};

17

18

19 return \Delta_{rnd}^{\lambda};

20 function rndPermPrefix(n, z)

Input: n, positive integer

Input: z, positive integer (z \le n)

Output: result, the first z elements of a permutation of [0, n-1] uniformly

chosen at random

result \leftarrow array of z elements;

21

perm \leftarrow empty associative array;

22

for i \leftarrow 0 \dots z - 1 do

23

j \leftarrow \text{random index between } i \text{ and } n-1;

24

if exists v \ s.t. \ \langle i, v \rangle \in perm \ then \ value\_i \leftarrow v \ ;

25

else value_i \leftarrow i;

26

if exists v \ s.t. \ \langle j, v \rangle \in perm \ then \ value\_j \leftarrow v ;

27

28

else value_{-j} \leftarrow j;

put (i, value_j) into perm;

29

put (j, value_i) into perm;

30

result[i] \leftarrow value\_j;

31

return result;

32

33 end

```

Point (i) is immediate: at each round, z traces are appended to  $\Delta^{\lambda}_{\rm rnd}$ , all the others are appended to  $\Delta^{\lambda}_{\rm tmp}$ , which becomes the input of the next round. Also, the algorithm terminates only if the  $\Delta^{\lambda}_{\rm tmp}$  produced at the previous round is empty.

To prove point (ii), for any p, q in [0, n-1], we compute the probability that trace  $\delta$  having position p in the input sequence (file  $\Delta^{\lambda}$ ) will have position q in the output sequence (file  $\Delta^{\kappa}_{rnd}$ ).

We omit to prove that function rndPermPrefix(n,z) actually computes the first z elements of a permutation of the integer interval [0,n-1] uniformly selected at random, as the function interrupts a well-known swap-based permutation algorithm as soon as the first z elements have been determined.

Given that, at each round  $r \geq 1$ , the main algorithm selects the z input traces which will have output positions (r-1)z to  $\min(n,rz-1)$ ,  $\delta$  is selected only at round  $r_{\delta} = \lceil (q+1)/z \rceil$ . Thus, the probability that  $\delta$ , having input position p, will have output position q is:

$$\Pr\left(\left(\bigcap_{r=1}^{r_{\delta}-1} \neg E_r\right) \cap O_{r_{\delta}}^{q'}\right) \tag{5}$$

where, for all r,  $\neg E_r$  denotes the event " $\delta$  is not selected at round r" and  $O_{r_\delta}^{q'}$  denotes the event " $\delta$  is the q'th trace selected in round  $r_\delta$ ," where  $q' = (q - z(r_\delta - 1))$ .

By the chain rule, (5) becomes:

$$\Pr\left(\neg E_{1}\right) \times \cdots \times \Pr\left(\neg E_{r_{\delta}-1} | \neg E_{r_{\delta}-2}, \dots \neg E_{1}\right)$$

$$\times \Pr\left(O_{r_{\delta}}^{q'} | \neg E_{r_{\delta}-1}, \dots \neg E_{1}\right).$$

$$\text{For all } 1 \leq r \leq r_{\delta} - 1:$$

$$\Pr\left(\neg E_{r} | \neg E_{r-1}, \dots \neg E_{1}\right) = \frac{n - z(r-1) - 1}{n - z(r-1)} \times \cdots$$

$$\times \frac{n - z(r-1) - z}{n - z(r-1) - (z-1)}$$

(6)

where, for all  $0 \le i < z$ , the ith factor is the number of ways we can choose a trace different from  $\delta$  out of n-z(r-1)-i (where n-z(r-1) is the number of traces still not selected at the beginning of round r). The expression simplifies to:

$$\Pr\left(\neg E_r \middle| \neg E_{r-1}, \dots \neg E_1\right) = \frac{n - zr}{n - z(r-1)}$$

and the product  $\Pr(\neg E_1) \times \cdots \times \Pr(\neg E_{r_{\delta}-1} | \neg E_{r_{\delta}-2}, \dots \neg E_1)$  is:

$$\Pr\left(\neg E_1\right) \times \dots \times \Pr\left(\neg E_{r_{\delta}-1} | \neg E_{r_{\delta}-2}, \dots \neg E_1\right) = \prod_{r=1}^{r_{\delta}-1} \frac{n-zr}{n-z(r-1)}$$

$$= \frac{n-z(r_{\delta}-1)}{n}.$$

(7)

As for  $\Pr\left(O_{r_{\delta}}^{q'}|\neg E_{r_{\delta}-1},\ldots \neg E_{1}\right)$ , i.e., the probability that  $\delta$  is the q'th selected trace in round  $r_{\delta}$  provided that it has not been selected in previous rounds, it can be computed as:

$$\frac{n - z(r_{\delta} - 1) - 1}{n - z(r_{\delta} - 1)} \times \dots \times \frac{n - z(r_{\delta} - 1) - (q' - 1)}{n - z(r_{\delta} - 1) - (q' - 2)} \times \frac{1}{n - z(r_{\delta} - 1) - (q' - 1)} = \frac{1}{n - z(r_{\delta} - 1)}$$

(8)

where, for all  $0 \le i < q'-1$ , the ith factor is the number of ways we can choose a trace different from  $\delta$  out of  $n-z(r_{\delta}-1)-i$  (where  $n-z(r_{\delta}-1)$  is the number of traces still not selected at the beginning of round  $r_{\delta}$ ). The last factor is the probability of selecting  $\delta$  (still unselected) out of  $n-z(r_{\delta}-1)-(q'-1)$  traces.

By (7) and (8), probability (6) evaluates to  $\frac{1}{n}$ , which is independent of p and q.  $\square$

# 6. Experimental results

In this section we evaluate the effectiveness of our random exhaustive SLFV (rSLFV) approach as follows. First, we evaluate the *overhead* due to the randomisation of disturbance traces needed to enable computation of Omission Probability (OP), by comparing our rSLFV approach with the Deterministic SLFV (dSLFV) approach of [8]. Second, we evaluate the behaviour of the coverage and the OP bound with respect to simulation time. Third, we evaluate speed-up and efficiency of our parallel approach.

# 6.1. Experimental setting

In this section we describe the case studies and the computational infrastructure we used in our experiments.

#### 6.1.1. Case studies

We experiment with two case studies, using two models included in the Simulink distribution, namely the Inverted Pendulum on a Cart (IPC) and the Fuel Control System (FCS).

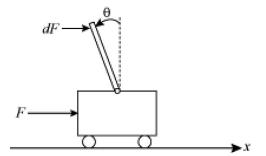

6.1.1.1. Inverted Pendulum on a Cart (IPC). The IPC is a control loop system where the controlled system is an inverted pendulum installed on a cart (see Fig. 7). The controller (actually a control software) senses the angular position  $\theta$  of the pendulum, and computes the force F to be applied to the cart to move it left or right

Fig. 7. Inverted Pendulum on a Cart (IPC) case study (from mathworks.com).

along the x axis. The goal is to keep the pendulum in its upright (vertical) unstable position. The physical constraint between the cart and the pendulum gives that both the cart and the pendulum have one degree of freedom each (x and  $\theta$ , respectively).

The controlled system consists of the cart and the pendulum, whereas the controller consists of the control software computing F from the plant outputs (x and  $\theta$ ). Accordingly, our overall System Under Verification (SUV) model consists of the controlled system and the controller, whose Simulink block diagram is shown in the upper box of Fig. 8.

The system level property that we verify is that after 2 s the pendulum is in upright position, i.e., angle  $\theta$  is always between [-0.1,0.1]. The monitor checking for this property is shown in the lower box of Fig. 8.

We introduce disturbances by injecting irregularities in the cart rail. We model such irregularities with a modification on the cart weight m with respect to its nominal value of 0.455 kg. For this, we define three disturbances representing normal rail operation (m = 0.455 kg), abnormal rail operation (m = 1.455 kg), and stressed rail operation (m = 2.455 kg).

We consider two disturbance models for the IPC,  $\mathcal{D}_{\mathrm{IPC}}^1$  and  $\mathcal{D}_{\mathrm{IPC}}^2$ . Model  $\mathcal{D}_{\mathrm{IPC}}^1$  has a horizon of h=90 and defines 3 208 276 disturbance traces. Model  $\mathcal{D}_{\mathrm{IPC}}^2$  is defined extending  $\mathcal{D}_{\mathrm{IPC}}^1$  with more complex operational scenarios and defines 35 641 501 disturbance traces over a horizon of h=200. For both models we set  $\tau$  (quantum between disturbances) to 0.1 s. A detailed description of  $\mathcal{D}_{\mathrm{IPC}}^1$  and  $\mathcal{D}_{\mathrm{IPC}}^2$  is not relevant for the evaluation of our experiments below. We only observe that, in our setting, the complexity of answering a System Level Formal Verification (SLFV) problem primarily depends on the number of disturbance traces to be simulated. Thus, the worst case for our approach is when all disturbance traces have to be simulated, i.e., when the answer to the SLFV problem is PASS. Indeed, both  $\mathcal{D}_{\mathrm{IPC}}^1$  and  $\mathcal{D}_{\mathrm{IPC}}^2$  satisfy this requirement.

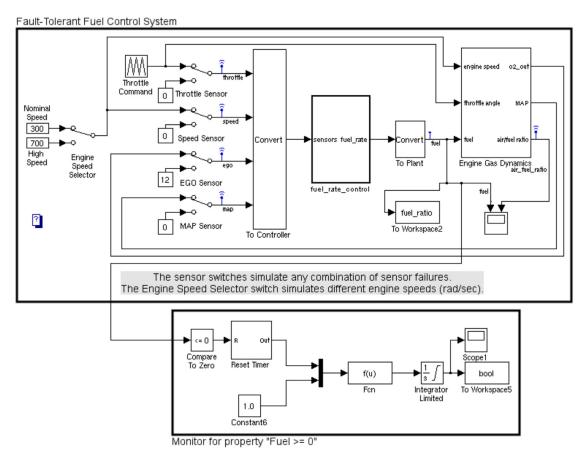

6.1.1.2. Fuel Control System (FCS). The FCS is a controller for a fault tolerant gasoline engine, which has also been used as a case study in [8,12,15–18]).

The FCS has four sensors: throttle angle, speed, EGO (measuring the residual oxygen present in the exhaust gas) and MAP (manifold absolute pressure). The goal of the control system is to maintain the air-fuel ratio (the ratio between the air mass flow rate pumped from the intake manifold and the fuel mass flow rate injected at the valves) close to the stoichiometric ratio of 14.6, which represents a good compromise between power, fuel economy, and emissions.

From the sensor measurements, the FCS estimates the mixture ratio and provides feedback to the closed-loop control, yielding an increase or a decrease of the fuel rate.

The FCS sensors are subject to faults (disturbances), and the whole control system can tolerate single sensor faults. In particular, if a sensor fault is detected, the FCS changes its control law

# Inverted Pendulum on a Cart Animation oportional Gair 0000 Integral Limited endulum Integrator 5.6662 7.12s Car 8+2 Feedforward Gain Discrete State Estimato fter 2 secs Reset Timer Integrator Fcn1 To Workspace5 Limited Constant6

Fig. 8. Simulink block diagram for Inverted Pendulum on a Cart (from mathworks.com) with an embedded property monitor.

by operating the engine with a higher fuel rate to compensate. In case two or more sensors fail, the FCS shuts down the engine, as the air-fuel ratio cannot be controlled.

Monitor for property "After 2 seconds angle is in [-0.1, 0.1]"

The control logic of the FCS is implemented by six automata, each one with a number of states ranging from two to five. The signal flow is further subdivided into three subsystems, which exhibit several different Simulink block types, involving arithmetic, lookup tables, integrators, filters and interpolation [19] (see [20] for more details).

We verify one of the system level specifications for such a model, namely: the *fuel\_air* model variable is never 0 for more than one second. Accordingly, our SUV consists of the Simulink FCS model along with a monitor for the property under verification (such a model is shown as Fig. 9).

We consider two disturbance models for the FCS,  $\mathcal{D}_{FCS}^1$  and  $\mathcal{D}_{FCS}^2$ . Model  $\mathcal{D}_{FCS}^1$  has a horizon of h=100 and defines 4 023 955 disturbance traces. Model  $\mathcal{D}_{FCS}^2$  is defined extending  $\mathcal{D}_{FCS}^1$  with more complex operational scenarios and defines 12 948 712 disturbance traces over a horizon of h=200. For both models we set  $\tau$  (quantum between disturbances) to 1 s. A detailed description of  $\mathcal{D}_{FCS}^1$  and  $\mathcal{D}_{FCS}^2$  is not relevant for the evaluation of our experiments below, and can be found in [8,21]. We only observe that, as it happens with our disturbance models for the IPC, for all disturbance traces entailed by  $\mathcal{D}_{FCS}^1$  and  $\mathcal{D}_{FCS}^2$ , the property to be verified is satisfied. This yields the worst scenario to answer our SLFV problem, as all traces need to be simulated.

# 6.1.2. Computational infrastructure

We ran experiments on multiple Linux PCs, each one equipped with 2 Intel Xeon 3.0 GHz CPUs with 4 cores each and 8 GB RAM. We executed 8 processes (optimisation and simulation) in parallel (one per available core) on each machine.

**Table 1** Disturbance trace generation.

| SUV | Dist. model                                                                                                     | #Traces  | Gen. time | File size |

|-----|-----------------------------------------------------------------------------------------------------------------|----------|-----------|-----------|

| IPC | $\mathcal{D}_{	ext{IPC}}^1$ $\mathcal{D}_{	ext{IPC}}^2$ $\mathcal{D}_{	ext{FCS}}^1$ $\mathcal{D}_{	ext{FCS}}^2$ | 3208276  | 0:9:58    | 4.6 GB    |

| IPC |                                                                                                                 | 35641501 | 7:28:24   | 107 GB    |

| FCS |                                                                                                                 | 4023955  | 0:28:39   | 3.5 GB    |

| FCS |                                                                                                                 | 12948712 | 4:45:47   | 39 GB     |

As, in a multi-core setting, the local disk may quickly become a performance bottleneck if heavily used by multiple processes, we have replaced it with 8 RAM disks of 500 MB each per machine, in order to store simulation states. Accordingly, we have used the multi-core version of the dSLFV optimiser of [8] as presented in [12]. Given that, in our case studies, the size of the simulation state files is of about 150–300 KB, this experimental setting allowed our optimiser to count on the possibility, for each simulator, to keep at most 1800 states simultaneously stored.

## 6.2. Disturbance trace generation and splitting

Along the lines of [8], we use CMurphi to generate the set of labelled admissible disturbance traces entailed by the disturbance model given as input.

Table 1 shows, for each of the four disturbance models we consider (two for IPC and two for FCS) the number of entailed disturbance traces (column #Traces), the time needed by CMurphi to generate them (column Gen. time) and the size of the file computed by our generator to store them (column File size).

We then split the generated sequences of disturbance traces into k slices, with k=128,256,512 to enable parallel computation on, respectively, 16, 32, 64 (8-core) machines. Splitting always takes negligible time.

Fig. 9. Simulink/Stateflow representation of the Fuel Control System (from mathworks.com) with an embedded property monitor.

#### 6.3. Computation of optimised simulation campaigns

Table 2 shows, for each of the disturbance models we consider, the time needed by our Random Sequence Generator module to enable anytime OP computation during the verification process (rSLFV) and the time needed to compute optimised simulation campaigns with (rSLFV) and without (dSLFV) trace order randomisation.

Column #Mach gives the number of machines we used in parallel. Column #Slices gives the overall number of slices in which the sequence of admissible disturbance traces has been partitioned (one per available core, i.e., 8 slices per machine). Column #Traces per slice shows the number of traces in any single slice (except the last slice, which has fewer traces when the overall number of traces is not a multiple of #Slices). Column group rSLFV shows the maximum overall time to compute the simulation campaign starting from a slice. This time is split into two parts: the time needed to execute the Random Sequence Generator module (column RSG) and the time needed to compute the simulation campaign starting from the randomised slice (column sim. camp. comp.). Column dSLFV shows the maximum time to compute the simulation campaign starting from a slice when no RSG is performed, thus no anytime OP computation is enabled. Column rSLFV overhead shows the difference between the rSLFV and dSLFV times.

It can be observed that our parallel approach to computation of optimised randomised simulation campaigns is able to effectively exploit parallelism in order to handle disturbance models entailing tens of millions of operational scenarios.

Also, Table 2 shows that the random sequence generation phase makes the rSLFV simulation campaign computation process longer than that for dSLFV (i.e., overhead is positive). The difference

is, however, *negligible* with respect to the whole verification time, which takes many hours, even for the massively parallel simulation of operational scenarios entailed by our smallest disturbance models, i.e.,  $\mathcal{D}_{\text{IPC}}^1$  for the IPC and  $\mathcal{D}_{\text{FCS}}^1$  for the FCS (see Section 6.4).

# 6.4. Execution of the simulation campaigns

Table 3 shows the execution time of the simulation campaigns generated by dSLFV and rSLFV.

As the exhaustive simulation of the traces generated by disturbance models  $\mathcal{D}_{\text{PC}}^2$ ,  $\mathcal{D}_{\text{FCS}}^2$  (entailing, respectively, 35 641 501 and 12 948 712 disturbance traces) would require a prohibitively long time, from now on we restrict ourselves to the simulation of the traces generated by  $\mathcal{D}_{\text{IPC}}^1$  and  $\mathcal{D}_{\text{FCS}}^1$  (which entail, respectively, 3 208 276 and 4 023 955 disturbance traces).

By enabling the computation of the OP during the simulation activity we have a quite significant increase of simulation time. However, such an overhead can be drastically reduced, or even neutralised, by using more parallel processes (higher values for k = #Slices). This behaviour is due to the fact that the rSLFV optimiser needs to compute a simulation campaign under the restriction that the number of states that the simulator can keep simultaneously stored is limited (to fit within the 500 MB of disk space available to each simulator instance). For high values of k=#Slices (e.g., k=512), this is not a big obstacle. On the other hand, for low values of k, the number of traces in each slice is higher and they share shorter common prefixes on average. Hence, a fully-optimised random order execution of them would need a too high number of simulation states to be simultaneously kept stored. As a consequence, the optimiser is forced to post free commands for many simulation states which would be needed again in

**Table 2**Overhead of enabling OP (rSLFV) with respect to dSLFV in the computation of simulation campaigns (time in h:m:s).

| #Mach. #Slices                              |                                                                | #Traces                                                                                                      | rSLFV                                                                                       |                                                                                                            |                                                                                      | dSLFV                                                                                                                | rSLFV                                                                                     |

|---------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                                             |                                                                | per slice                                                                                                    | RSG                                                                                         | sim.camp.comp.                                                                                             | Total                                                                                | sim.camp.comp.                                                                                                       | overhead                                                                                  |

| 1                                           | 8                                                              | 401 035                                                                                                      | 0:0:21                                                                                      | 1:8:52                                                                                                     | 1:9:13                                                                               | 0:8:53                                                                                                               | 1:0:20                                                                                    |

| 2                                           | 16                                                             | 200 518                                                                                                      | 0:0:11                                                                                      | 0:11:57                                                                                                    | 0:12:9                                                                               | 0:4:36                                                                                                               | 0:7:32                                                                                    |

| 4                                           | 32                                                             | 100 259                                                                                                      | 0:0:5                                                                                       | 0:6:33                                                                                                     | 0:6:38                                                                               | 0:2:23                                                                                                               | 0:4:14                                                                                    |

| 8                                           | 64                                                             | 50 130                                                                                                       | 0:0:3                                                                                       | 0:2:50                                                                                                     | 0:2:53                                                                               | 0:1:14                                                                                                               | 0:1:39                                                                                    |

| 16                                          | 128                                                            | 25 065                                                                                                       | 0:0:2                                                                                       | 0:1:23                                                                                                     | 0:1:26                                                                               | 0:0:38                                                                                                               | 0:0:47                                                                                    |

| 32                                          | 256                                                            | 12 533                                                                                                       | 0:0:1                                                                                       | 0:1:19                                                                                                     | 0:1:21                                                                               | 0:0:20                                                                                                               | 0:1:1                                                                                     |

| 64                                          | 512                                                            | 6267                                                                                                         | 0:0:1                                                                                       | 0:0:21                                                                                                     | 0:0:23                                                                               | 0:0:11                                                                                                               | 0:0:12                                                                                    |